O impacto da qualidade do wafer de silício no desempenho e na confiabilidade dos semicondutores

1 Introdução

O mercado de semicondutores continua a crescer à medida que a economia se recupera. Aplicativos emergentes, como 5G e veículos de energia nova, trazem uma nova rodada de crescimento para o setor global de semicondutores. Dados da World Semiconductor Trade Statistics Organization (WSTS) mostram que o tamanho do mercado global de semicondutores em 2022 crescerá 3,3% em relação ao ano anterior, atingindo um recorde de US$ 574 bilhões.

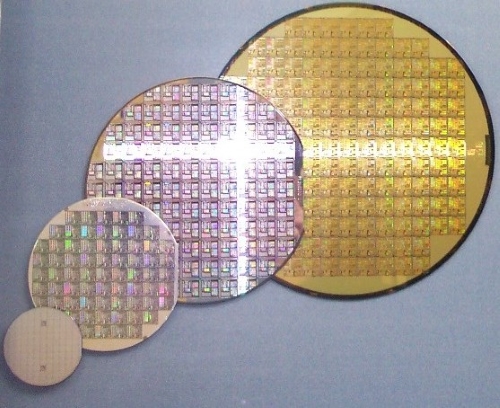

Como material de base de chips semicondutores, o setor de wafer de silício também entrará em um desenvolvimento de alta velocidade. Como parte da recuperação da demanda por produtos eletrônicos de consumo e do aumento da demanda por surtos de IA, a fábrica de wafer de 12 polegadas teve uma recuperação gradual no segundo semestre de 2023. Com o desenvolvimento acelerado das empresas líderes e a recuperação gradual da demanda final, o segmento terá um crescimento de dois dígitos em 2024.

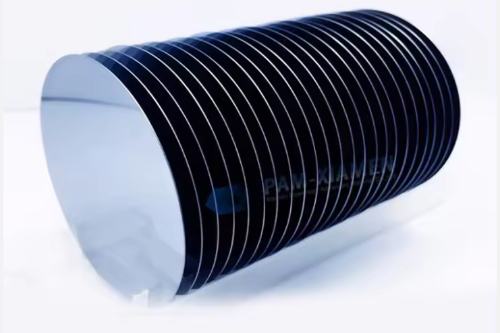

Como material básico essencial na fabricação de semicondutores, a qualidade do cristal das pastilhas de silício (Fig. 1) afeta diretamente as propriedades do dispositivo semicondutor acabado. O efeito da qualidade da rede e dos defeitos nos limites dos grãos sobre a mobilidade dos elétrons das pastilhas de silício afeta diretamente a velocidade e o consumo de energia do dispositivo e pode aumentar a corrente de fuga do dispositivo. A planicidade e o grau de contaminação na superfície de uma pastilha de silício podem ter um impacto significativo nas principais etapas, como litografia, deposição de filme fino e gravação. As impurezas e a dopagem nas pastilhas de silício podem levar ao aumento do aprisionamento de elétrons, à redução do tempo de vida dos portadores e ao desvio dos parâmetros do dispositivo. Além disso, podem ser introduzidas tensões de temperatura e pressão durante a preparação da pastilha de silício e o processamento subsequente, afetando a estabilidade mecânica e as propriedades elétricas dos cristais.

2 Principais fatores que determinam a qualidade dos wafers de silício

2.1 Estrutura cristalina: Pureza do cristal único de silício, defeitos de cristal

Os principais fatores que determinam a qualidade das pastilhas de silício em termos de estrutura cristalina são, na maioria das vezes, mencionados como pureza do cristal e defeitos do cristal.

1. Pureza do cristal: A pureza do silício de cristal único é fundamental para suas propriedades elétricas. O silício industrial típico (99,0-99,9%) não tem propriedades semicondutoras, mas quando purificado a uma pureza muito alta (99,999999999%), ele apresenta excelentes propriedades semicondutoras. O silício monocristalino de alta qualidade geralmente atinge 99,999999999% (9 de 9) ou mais no nível eletrônico.

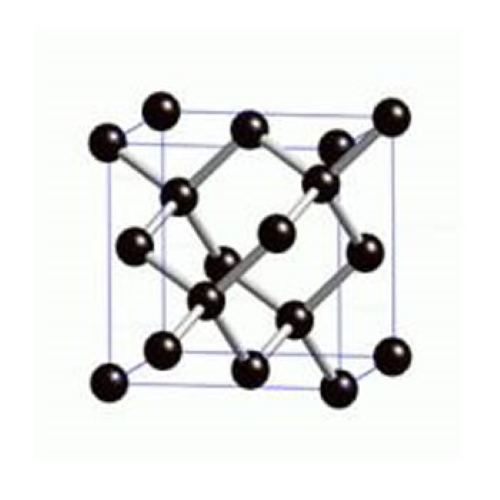

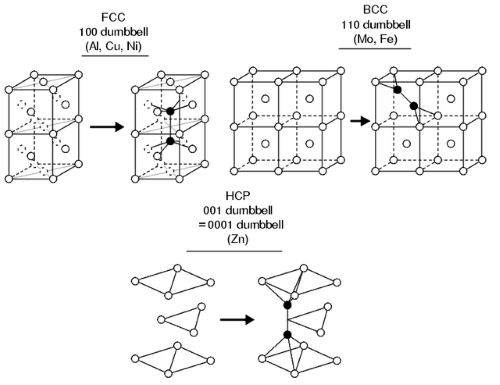

2. Defeitos cristalográficos: O arranjo espacial do cristal real e o arranjo espacial ideal são diferentes, pois não podem ser feitos de acordo com o arranjo periódico regular ideal absoluto (Fig. 2). Em vez disso, no arranjo, há irregularidades e aberrações, desvios da matriz espacial ideal. Essas estruturas ou regiões que se desviam da matriz de pontos são comumente conhecidas como defeitos de cristal.

Entre eles, a luxação é um defeito de cristal muito importante. O deslocamento de um cristal é uma linha muito longa em torno da qual os átomos em uma determinada faixa são regularmente desalinhados, deixando sua posição de equilíbrio original, por isso é chamado de deslocamento.

2.2 Qualidade da superfície: Planicidade, rugosidade, contaminação por partículas

1. Contaminação da superfície: Esse defeito se refere a materiais estranhos, como poeira, partículas e poluentes presos à superfície do wafer, provenientes dos resíduos gerados nos processos de corte, polimento, limpeza, gravação etc., ou da poeira no ar, ou do resíduo de reagentes químicos. Essas redundâncias afetam a planicidade e a limpeza do wafer, bem como a qualidade dos processos subsequentes de litografia, dopagem e outros, o que pode levar a defeitos na estrutura do circuito integrado ou a alterações nas características elétricas do chip.

2. Danos mecânicos: Esse defeito refere-se à superfície do wafer ou à borda dos arranhões, lascas, descascamento e outros fenômenos, no corte, polimento, manuseio e outros processos do wafer gerados pelo impacto ou atrito, ou a qualidade da lâmina ou os parâmetros do inadequado podem levar a uma redução na planicidade da superfície. Esses danos mecânicos afetam a integridade e a estabilidade do wafer e podem levar à quebra ou ao desprendimento do chip.

2.3 Precisão dimensional: Diâmetro do wafer, espessura, empenamento

O tamanho e a espessura dos wafers não são escolhidos arbitrariamente, mas se baseiam nos requisitos do processo e nas propriedades físicas. Quando o tamanho do wafer se torna maior, a espessura do wafer é aumentada de forma correspondente para manter a resistência mecânica e o empenamento e, ao mesmo tempo, evitar danos causados por estresse ou flexão durante o processamento. Os wafers são submetidos a vários tratamentos físicos e químicos no processo de fabricação, incluindo gravação, implantação de íons, oxidação, difusão etc. Esses processos podem fazer com que o wafer se torne mais rígido. Esses processos podem fazer com que o wafer seja submetido a estresse mecânico e, se o wafer for muito fino, pode fraturar ou quebrar. Os wafers precisam ser manuseados e posicionados durante o processamento. Se o wafer for muito fino, ele poderá ser dobrado, afetando a precisão do processamento.

3 Como os fatores de qualidade do wafer de silício afetam o desempenho dos dispositivos semicondutores

3.1 Estrutura cristalina, defeitos de rede

Os deslocamentos mais comuns nos defeitos da rede têm um impacto significativo nas propriedades elétricas dos monocristais de silício. Por exemplo, os deslocamentos afetam a resistividade e a concentração de portadores, diminuem a vida útil dos portadores minoritários e reduzem a mobilidade dos elétrons.

1. Efeito de resistividade: Os deslocamentos introduzem campos de tensão localizados e não uniformidades dentro do cristal, levando ao aumento da dispersão de elétrons e buracos. Essa dispersão leva ao bloqueio da migração de portadores, o que aumenta a resistividade do material.

2. Efeitos de concentração de portadores: Os deslocamentos podem introduzir átomos de impureza adicionais ou alterar a disposição dos átomos na estrutura, mudando assim a concentração de portadores do material semicondutor. Por exemplo, um campo de tensão localizado próximo a um deslocamento pode fazer com que a posição dos átomos seja deslocada ou deformada, o que, por sua vez, afeta a geração e a supressão de portadores.

3. Redução da vida útil do portador minoritário: Os deslocamentos aumentam a complexidade do portador no material. Nos semicondutores, a complexação do portador leva à redução da vida útil dos portadores minoritários (por exemplo, elétrons ou buracos dentro do comprimento de difusão dos portadores minoritários). O campo de tensão localizado e a não uniformidade introduzida pelos deslocamentos podem aumentar a interação do portador e promover o processo de composição.

4. Redução da mobilidade dos elétrons: Os deslocamentos causam distorções e não uniformidades na estrutura do cristal, o que pode impedir o movimento dos portadores dentro do cristal. Especialmente no caso dos elétrons, eles são dispersos na estrutura por defeitos como deslocamentos e limites de grãos, o que reduz a mobilidade dos elétrons.

3.2 Planicidade da superfície

A planicidade da superfície de um wafer de silício tem um efeito em cascata nos dispositivos semicondutores. Ela não só afeta diretamente a qualidade da superfície de contato em contato com outros materiais ou dispositivos, como eletrodos de metal e materiais de embalagem. A qualidade da superfície de contato afeta diretamente o valor da resistência de contato, e uma superfície de contato irregular sob a influência de forças externas para produzir várias alterações de dados também terá um impacto sobre o desempenho e a confiabilidade do dispositivo.

Além disso, a planicidade da superfície do wafer de silício, a contaminação e outras condições da superfície também afetarão o uso da fotolitografia e da tecnologia de gravação para definir a estrutura. A tecnologia de gravação e a fotolitografia são usadas com frequência no processo de fabricação de dispositivos semicondutores para gravar a estrutura e o padrão do dispositivo. A condição da superfície do wafer de silício afeta diretamente a precisão da fotolitografia e da gravação, a qualidade e a uniformidade dos gráficos e a forma e o tamanho do dispositivo produzido são decisivos.

Como as pastilhas de silício são um importante material de substrato para a deposição de filmes finos, a planicidade de sua superfície afeta diretamente a qualidade do filme depositado na superfície. Os defeitos e a contaminação na superfície dos wafers de silício podem levar à deposição desigual do filme, inconsistências na espessura do filme, bolhas, rachaduras e outros defeitos, afetando assim o desempenho e a estabilidade do dispositivo.

3.3 Limites de grãos e impurezas

A resistividade de um semicondutor é muito sensível à quantidade de impurezas que ele contém. Mesmo impurezas minúsculas podem afetar seriamente as propriedades elétricas do silício, como a condutividade e a mobilidade dos portadores. Em particular, algumas impurezas, como ferro, cobre e magnésio, têm um grande impacto sobre as propriedades elétricas. A presença de impurezas pode levar à dispersão de elétrons e à não uniformidade local no cristal, reduzindo assim o desempenho e a confiabilidade do dispositivo. As alterações no conteúdo de impurezas podem causar mudanças significativas na resistividade dos materiais semicondutores. Por exemplo, quando a concentração de impurezas de fósforo no silício varia na faixa de 1021-1012 cm-3, sua resistividade muda de 10-4 Ω.cm para 104 Ω.cm. Não há muitos materiais cuja resistividade possa variar em uma faixa tão ampla, o que mostra que o conteúdo de impurezas dos semicondutores é um dos principais fatores na determinação de sua resistividade.

3.4 Tamanho, espessura e empenamento do wafer

No processo de fabricação, quanto maior o diâmetro do tamanho do wafer de silício, sem dúvida, mais favorável é para o fabricante. Nos wafers de silício de grande tamanho e grande diâmetro, é possível produzir mais dispositivos de chip, a eficiência da produção de equipamentos pode ser efetivamente melhorada; ao mesmo tempo, a borda do material desperdiçado será reduzida para diminuir os custos adicionais, além de melhorar a taxa de reutilização do equipamento.

Mas o tamanho do wafer de silício não é uma decisão arbitrária, ele depende da capacidade de processamento do equipamento de produção, porque o próprio material desempenha o papel de estresse, quando o tamanho do wafer aumenta, sua espessura precisará ser aumentada de acordo, para manter a estabilidade estrutural do material, caso contrário, o tamanho da espessura grande e fina do material do wafer será um aumento correspondente na espessura do material do wafer, que até aparecerá perda de fratura e outros fenômenos.

4 Como a qualidade do wafer de silício afeta a confiabilidade dos semicondutores

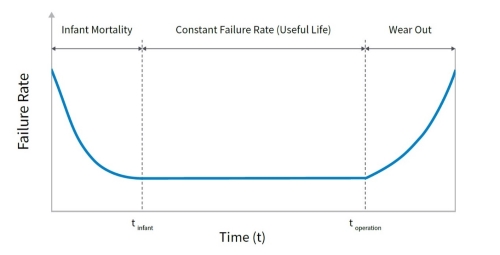

4.1 Efeito da densidade de defeitos na vida útil do dispositivo

A vida útil de um dispositivo semicondutor é determinada principalmente por sua vida física e por sua vida útil de manutenção. A vida física refere-se ao tempo em que um dispositivo semicondutor falha devido ao envelhecimento do material ou ao desgaste em condições normais de operação. Os defeitos em wafers de silício podem acelerar o processo de envelhecimento do material, fazendo com que o dispositivo falhe em um período mais curto. Ao mesmo tempo, os defeitos também podem levar a vazamento de corrente, estabilidade térmica reduzida e outros problemas, afetando ainda mais a vida útil do dispositivo.

A vida útil do reparo é o tempo em que um dispositivo semicondutor pode ser reparado e continua a operar normalmente após uma falha. No entanto, se a densidade de defeitos das pastilhas de silício for muito alta, pode ser difícil restaurar o desempenho original do dispositivo durante o processo de reparo ou tornar o custo do reparo muito alto, reduzindo assim sua vida útil.

Os defeitos nas pastilhas de silício também afetam a confiabilidade dos dispositivos semicondutores. Os defeitos na estrutura cristalina fazem com que as partículas saiam da posição ideal da estrutura cristalina, o que leva à colagem em diferentes posições e a mudanças na estrutura cristalina, que se manifesta como tensão irregular, o que pode levar à instabilidade ou à falha repentina do dispositivo durante a operação, afetando assim a estabilidade de todo o sistema eletrônico.

4.2 Relação da qualidade do wafer com a corrente de fuga e a tensão de ruptura

A corrente de fuga é a corrente que não deveria fluir em um dispositivo semicondutor sob tensão operacional normal. Quando há defeitos em um wafer de silício, como impurezas, distorções de rede, microfissuras etc., esses defeitos, bem como as impurezas, especialmente as partículas de impureza com propriedades condutoras, podem formar canais condutores que fazem com que a corrente flua onde não deveria, gerando assim a corrente de fuga. A presença de corrente de fuga não só aumenta o consumo de energia do dispositivo, mas também pode fazer com que a temperatura do dispositivo aumente, afetando ainda mais o desempenho e a vida útil do dispositivo.

A tensão de ruptura é a tensão máxima que um dispositivo semicondutor pode suportar em condições normais de operação. Além dessa tensão, o dispositivo pode sofrer uma pane, que é um aumento repentino da corrente, resultando em danos ao dispositivo. Os defeitos nas pastilhas de silício podem reduzir a tensão de ruptura de um dispositivo porque pode haver uma concentração de campos elétricos ou fragilidade estrutural nos defeitos, o que permite que o dispositivo se rompa em tensões mais baixas. Assim, a qualidade da pastilha de silício tem um efeito significativo sobre a tensão de ruptura.

5 Fabricação de wafer de silício e controle de qualidade

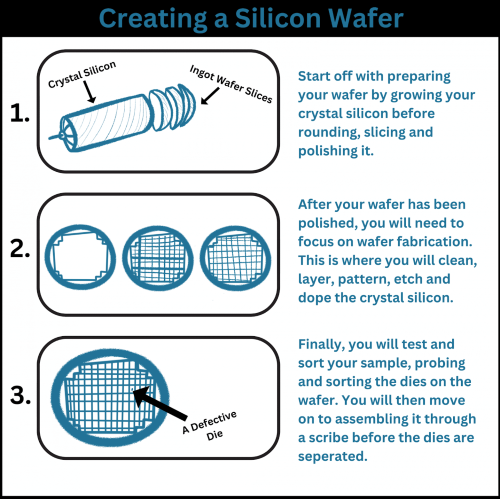

5.1 Tecnologia de crescimento de cristais para pastilhas de silício

Atualmente, o método Lift-off é comumente usado para o crescimento de cristais de silício. O cadinho é preenchido com silício e aquecido de modo que a temperatura no cadinho seja mantida em 1685°C. Essa temperatura é cerca de 100°C acima da temperatura do cadinho. Essa temperatura está cerca de 100°C acima do ponto de fusão do silício sozinho, portanto, o silício sozinho no cadinho está em um estado fundido. Na parte superior do cadinho, há uma haste de elevação e um dispositivo mecânico para fazer com que a haste de elevação se eleve e gire livremente. Um pequeno pedaço de silício monocristalino é imerso no cadinho, fixando-o na parte superior da alavanca. Esse cristal único de silício atua como uma "semente" e atrai os átomos de silício ao redor para que se organizem em torno dele e formem um cristal. O cristal cresce à medida que é lentamente puxado e girado, e as partes que são retiradas pertencem todas ao mesmo cristal único. O grande cristal único tem 200 milímetros de diâmetro, o que é mais grosso que seu braço. Esse cristal não tem interface, nem defeitos, e pode ser considerado o cristal único mais perfeito que o ser humano pode produzir. Para garantir a pureza do material e evitar a nucleação não uniforme, todas as operações devem ser realizadas sob vácuo ou proteção de gás inerte. Para evitar a ocorrência de deslocamentos no cristal, o método tradicional de levantamento de silício monocristalino consiste em fazer um pescoço fino no início do crescimento da cristalização, o que é chamado de "método de necking". Devido à força do pescoço, é difícil levantar o silício monocristalino que pesa mais de 100 quilos. Os cientistas adicionaram uma quantidade considerável de boro no cristal de semente, o que aumentou muito a resistência do cristal de semente, evitando o deslocamento do cristal e, portanto, não é mais necessário produzir um pescoço de 3 mm de diâmetro. Esse novo método substituirá o uso de 30 anos de método de pescoço, não só é capaz de produzir silício monocristalino grande, mas também de reduzir o tempo de crescimento do cristal e melhorar o rendimento, para a produção barata de circuitos integrados de escala ultragrande necessários para fornecer a possibilidade de silício monocristalino grande.

O crescimento do wafer requer que o polissilício seja colocado no cadinho de quartzo do forno, no vácuo ou passe gás inerte após a fusão. Depois que o silício fundido é estabilizado, os cristais únicos podem ser puxados, e um pedaço de cristal semente que já determinou a direção interna do cristal é usado como guia na superfície do líquido. Com o controle da altura da superfície líquida do cadinho, da temperatura da interface sólido-líquido e da velocidade de rotação do cristal de semente, o silício é transformado de líquido novamente em sólido com uma direção cristalina interna uniforme para desenvolver cristais únicos de grande diâmetro. O processo de ajuste automático e a velocidade de elevação são controlados por computadores, o que garante o crescimento isotrópico do silício monocristalino.

5.2 Tecnologia de tratamento de superfície para wafers de silício

Após o corte, os wafers precisam passar pelo tratamento de superfície para garantir a planicidade da superfície do wafer e a ausência de contaminação por impurezas. Os métodos de tratamento mais usados são a fotolitografia, a gravação, etc. Há também algumas técnicas de limpeza, como a limpeza por plasma, que pode não apenas limpar a superfície do wafer, mas também melhorar a atividade da superfície, melhorar a capacidade de ligação da superfície do material, melhorar a capacidade de soldagem, a hidrofilicidade e assim por diante.

Além disso, há alguns métodos inovadores de tratamento, como colocar o wafer em uma câmara de reação com um gás de reação; reagir o gás de reação com os óxidos na superfície do wafer para formar um produto de reação; e recozer o wafer pelo menos duas vezes para decompor e remover o produto de reação. O método de tratamento de superfície permite que os produtos de reação gerados no processo de tratamento de superfície sejam decompostos várias vezes por meio do recozimento do wafer várias vezes, e cada tratamento de recozimento decompõe os produtos de reação de modo que a espessura dos produtos de reação continue a diminuir, e, ao mesmo tempo, reduz a dificuldade de decomposição dos produtos da reação devido à espessura excessiva dos produtos da reação, facilitando a decomposição dos produtos da reação na superfície do wafer e reduzindo o número de vezes que o wafer é recozido durante o processo de tratamento de superfície e reduzindo o número de vezes que o método de tratamento de superfície é recozido. Isso reduz a quantidade de resíduos de produtos de reação na superfície do wafer durante o processo de tratamento de superfície.

5.3 Técnicas de inspeção da qualidade do wafer de silício

Devido à presença de defeitos no wafer, podem ocorrer falhas no chip durante o teste de integridade funcional de todos os chips em um wafer. Os engenheiros de chips marcam os resultados dos testes com cores diferentes para distinguir a localização dos chips. Sob a influência de diferentes processos operacionais, padrões espaciais específicos são gerados no wafer. Hansen et al., em 1997, observaram que os chips defeituosos geralmente apresentam fenômenos de agregação ou exibem alguns padrões sistemáticos, e esses padrões defeituosos geralmente contêm informações necessárias sobre as condições do processo. O mapa do wafer não apenas reflete a integridade do chip, mas também descreve com precisão as informações de localização espacial correspondentes aos dados de defeitos. O mapa de wafer pode mostrar a dependência espacial em todo o wafer, e os engenheiros de chip podem, com frequência, rastrear a causa dos defeitos e resolver problemas com base no tipo de defeito. Para padrões de wafer com grandes áreas, pequenos tamanhos de recursos, baixas densidades e baixa integração, os caminhos de litografia podem ser observados com um microscópio eletrônico, e a detecção de traços pode ser realizada diretamente. Um sistema de processamento de sinal de imagem também pode ser usado para detecção, em que o sinal de imagem é decomposto em diferentes subbandas de frequência por filtros e, em seguida, a média, o desvio padrão e outras estatísticas, como coeficientes de wavelet, são detectados e calculados para detectar anomalias.

6 Conclusão

Como um material fundamental na fabricação de semicondutores, a qualidade do cristal das pastilhas de silício afeta diretamente as propriedades dos dispositivos semicondutores acabados. Os avanços tecnológicos nos processos de produção e teste levaram a um aprimoramento gradual da pureza e da precisão das pastilhas de silício, que serão usadas em uma variedade maior de aplicações e em materiais mais precisos no futuro. Para uma melhor experiência de aplicação, a Stanford Advanced Materials não apenas fornecerá produtos de wafer de silício de alta qualidade, mas também serviços completos, incluindo consultoria e processamento pós-venda.

Leitura relacionada:

Wafer de arseneto de gálio VS. Wafer de silício

Crescimento e adesão de grafeno a pastilhas de silício

Referências:

[1]Masataka H ,Daiki T ,Oga N , et al. Experimental study on the effect of impurity concentration on phonon and electronic transport properties of single-crystal silicon[J]. Results in Physics,2023,47.

[2]Martin M ,P. P M ,Yi S B , et al. Effect of grain boundary scattering on carrier mobility and thermoelectric properties of tellurium incorporated copper iodide thin films[J]. Surfaces and Interfaces,2023,41.

Barras

Barras

Miçangas e esferas

Miçangas e esferas

Parafusos e porcas

Parafusos e porcas

Cadinhos

Cadinhos

Discos

Discos

Fibras e tecidos

Fibras e tecidos

Filmes

Filmes

Flocos

Flocos

Espumas

Espumas

Folha de alumínio

Folha de alumínio

Grânulos

Grânulos

Favos de mel

Favos de mel

Tinta

Tinta

Laminado

Laminado

Nódulos

Nódulos

Malhas

Malhas

Filme metalizado

Filme metalizado

Placa

Placa

Pós

Pós

Vara

Vara

Folhas

Folhas

Cristais individuais

Cristais individuais

Alvo de pulverização

Alvo de pulverização

Tubos

Tubos

Lavadora

Lavadora

Fios

Fios

Conversores e calculadoras

Conversores e calculadoras

Chin Trento

Chin Trento