Comparação entre SOI e wafers de silício: O que é melhor para seu projeto de semicondutores?

1 Introdução

O SOI é um material semicondutor com uma estrutura de substrato de silício com camada de silício isolante e camada de silício em camadas. Em comparação com os wafers de silício, que são comumente usados em dispositivos semicondutores, há diferenças significativas entre os dois em termos de estrutura do material, características de desempenho, áreas de aplicação etc.

A estrutura SOI melhora o desempenho e a confiabilidade do dispositivo por meio da estrutura em camadas de silício, camada isolante e substrato de silício, mas o custo de fabricação é mais alto. Os wafers de silício tradicionais, por outro lado, têm custos de fabricação mais baixos e são adequados para uma ampla gama de fabricação de circuitos integrados.

![]()

2 O que é SOI?

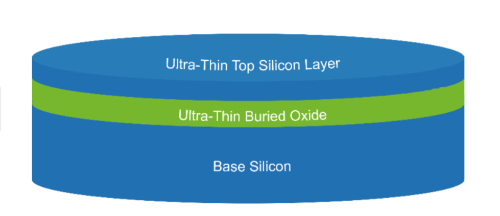

SOI significa Silicon-On-Insulator (silício sobre isolador). No SOI, a superfície de um chip de silício é coberta com um material isolante (geralmente dióxido de silício), sobre o qual uma camada de silício é então cultivada. Essa estrutura cria uma estrutura em camadas de camada de silício - camada isolante - substrato de silício.

2.1 A estrutura da SOI

A estrutura de um SOI (Silicon-On-Insulator) consiste nas seguintes partes principais:

- Camada de Si: Na parte superior da estrutura SOI, há uma camada de cristais de silício (Si) que normalmente têm as propriedades eletrônicas e as características do dispositivo desejadas. Essa camada pode ser preparada usando técnicas padrão de crescimento de wafer de silício.

- Camada isolante: Abaixo da camada de Si há um material isolante, geralmente dióxido de silício (SiO2). O objetivo da camada isolante é isolar a camada de silício acima do substrato de silício abaixo, reduzindo assim a interferência entre os transistores.

- Substrato de silício: O substrato de silício é a parte inferior da estrutura SOI e geralmente é o principal substrato de suporte para o wafer. O substrato de silício é geralmente silício cristalino, que fornece suporte mecânico e estabilidade à estrutura SOI.

2.2 A classificação da SOI

Há diversas variantes diferentes da tecnologia SOI. As SOIs podem ser classificadas de acordo com diferentes critérios, dependendo de sua estrutura e de sua finalidade.

2.2.1 Classificação por tipo de estrutura

SOI comum (c-SOI): A SOI comum é uma das estruturas SOI mais comuns, também conhecida como SOI completa. Ela utiliza o método comum de fabricação de SOI, que consiste em depositar uma camada isolante (geralmente dióxido de silício) na superfície de um wafer de silício e, em seguida, desenvolver uma camada de silício sobre ela. Em uma SOI comum, a espessura da camada de silício é geralmente comparável à espessura da camada isolante, formando uma estrutura de substrato de silício-camada isolante-camada de silício.

SOI parcial (p-SOI): A SOI parcial difere da SOI regular pelo fato de a espessura da camada de silício ser mais fina, apenas uma fração da espessura da camada isolante. Em uma SOI parcial, a espessura da camada de silício é normalmente menor do que a espessura da camada isolante, o que dá à estrutura da SOI parcial uma camada de silício mais fina.

SOI reversa (r-SOI): A SOI reversa é uma estrutura SOI especial que é diferente da SOI normal e da SOI parcial. Na SOI reversa, a camada de silício é removida do substrato e recolocada na camada isolante. Essa estrutura permite que o transistor fique localizado acima da camada isolante e que o substrato de silício fique localizado abaixo da camada isolante, alterando assim a topologia da estrutura SOI convencional.

Essas diferentes variantes de SOI oferecem diferentes vantagens e aplicabilidade em aplicações específicas. As SOIs comuns são comumente usadas em aplicações de alto desempenho e baixa potência, enquanto as SOIs parciais são mais adequadas para algumas fabricações específicas de dispositivos de radiofrequência (RF), e as SOIs invertidas oferecem benefícios adicionais em aplicações específicas, como dispositivos de alta velocidade e baixa perda.

2.2.2 Classificação por tipo de substrato de cristal

Silício sobre isolador (SIMOX-SOI): O SIMOX (Separation by IMplantation of OXygen) é um método comum de preparação de SOI, também conhecido como silício sobre isolador. Na preparação SIMOX-SOI, os íons de oxigênio são injetados no wafer e, em seguida, tratados termicamente para fazer com que os íons de oxigênio formem uma camada isolante de óxido de silício no wafer, resultando na formação da estrutura SOI.

SOI ultrafina (UTSOI): A SOI ultrafina é um tipo especial de estrutura SOI caracterizada por uma camada de silício muito fina, geralmente entre alguns nanômetros e dezenas de nanômetros. O método de preparação da UTSOI geralmente envolve técnicas especiais de crescimento ou decapagem para formar uma camada muito fina de silício em um substrato de silício para realizar a estrutura SOI.

SOI epitaxial (Epi-SOI): A Epi-SOI é um método de formação de estruturas SOI por meio do crescimento de uma camada de silício epitaxial em um substrato de silício. Na Epi-SOI, a camada de silício epitaxial é desenvolvida em um substrato de silício e, normalmente, tem a mesma estrutura cristalina do substrato, mas com uma camada isolante entre a camada de silício e o substrato.

A SIMOX-SOI é comumente usada na fabricação de CIs, a UTSOI é comumente usada para aplicações de alto desempenho e baixo consumo de energia, como comunicações móveis e dispositivos de RF, enquanto a Epi-SOI oferece melhor qualidade de cristal e controle estrutural para necessidades específicas de fabricação de dispositivos.

2.2.3 Classificação de acordo com a espessura da camada de silício

SOI de película fina: na SOI de película fina, a espessura da camada de silício geralmente fica entre dezenas de nanômetros e centenas de nanômetros. Esse tipo de estrutura SOI é frequentemente usado para fabricar dispositivos ultrafinos, como dispositivos eletrônicos de baixa potência, dispositivos optoeletrônicos e assim por diante. Normalmente, as SOIs de camada fina são preparadas usando uma série de etapas de processamento de precisão, incluindo técnicas como polimento químico-mecânico (CMP) e injeção e remoção de íons de hidrogênio.

SOI de película espessa: na SOI de película espessa, a espessura da camada de silício costuma ser de várias centenas de nanômetros ou mais. Esse tipo de estrutura SOI é normalmente usado para fabricar dispositivos de circuito integrado tradicionais, como microprocessadores, memórias etc. As SOIs de camada espessa geralmente são preparadas usando diferentes técnicas, como SIMOX, Unibond e Smart Cut. Essas técnicas permitem a preparação de camadas de silício com grandes espessuras para atender às necessidades da fabricação de circuitos integrados convencionais.

2.2.4 Classificação pelo método de controle de carga para transistores

SOI totalmente esgotado (FD-SOI): No FD-SOI, toda a camada de silício está em um estado esgotado, o que significa que a carga do transistor é totalmente controlada pela porta acima e não é afetada pelo substrato inferior. Ao controlar com precisão a espessura da camada de silício e as características da camada isolante, é possível obter uma camada inteira de silício em um estado esgotado. Essa estrutura proporciona melhor controle de carga e menor corrente de fuga. A SOI totalmente empobrecida é geralmente considerada uma tecnologia de semicondutores de última geração com maior desempenho e menor consumo de energia e, portanto, está recebendo cada vez mais atenção no projeto e na fabricação de chips.

SOI parcialmente esgotada (pFD-SOI): Na SOI parcialmente empobrecida, uma parte da camada de silício está em um estado empobrecido, enquanto outra parte permanece em um estado não empobrecido. Normalmente, com projeto e processo adequados, é possível perceber que apenas uma parte da camada de silício (geralmente a parte superior) está em um estado esgotado. A SOI parcialmente esgotada pode ser usada em aplicações de alto desempenho e baixo consumo de energia, como comunicações móveis, dispositivos de radiofrequência (RF) e outras áreas. Ele oferece oportunidades de melhor controle de carga e otimização de desempenho.

A tabela abaixo mostra as várias estruturas SOI, suas características definidoras e suas aplicações típicas, fornecendo uma visão geral abrangente das diferenças entre cada tipo de SOI.

A Stanford Advanced Materials (SAM) e outros fornecedores confiáveis oferecem wafers SOI de vários tamanhos e tipos. Essas opções são feitas sob medida para atender às suas especificações precisas.

Tabela 1 Comparação de diferentes tipos de wafers SOI

|

Classificação |

Tipo |

Breve descrição e aplicações |

|

Tipo de estrutura |

c-SOI |

Espessura da camada de silício semelhante à da camada isolante. Usado em aplicações de alto desempenho e baixo consumo de energia. |

|

p-SOI |

Camada de silício mais fina em comparação com a camada isolante. Adequado para fabricação de dispositivos de RF específicos. |

|

|

r-SOI |

Camada de silício recolocada acima da camada isolante, invertendo a estrutura. Para dispositivos de alta velocidade e baixa perda. |

|

|

Tipo de substrato de cristal |

SIMOX-SOI |

Os íons de oxigênio formam uma camada isolante de óxido de silício. Comum na fabricação de CIs. |

|

UTSOI |

Camada de silício ultrafina para aplicações de alto desempenho e baixo consumo de energia, como dispositivos móveis e de RF. |

|

|

Epi-SOI |

Camada epitaxial cultivada em um substrato de silício para dispositivos que precisam de melhor qualidade de cristal. |

|

|

Espessura da camada de silício |

SOI de filme fino |

Camada de silício com espessura de dezenas a centenas de nanômetros. Para dispositivos eletrônicos e optoeletrônicos de baixa potência. |

|

SOI de filme espesso |

Camada de silício com várias centenas de nanômetros de espessura. Usada em dispositivos de CI tradicionais, como microprocessadores. |

|

|

Método de controle de carga para transistores |

FD-SOI |

Toda a camada de silício é esgotada para controle total de carga. Destina-se à tecnologia de última geração de alto desempenho e baixo consumo de energia. |

|

pFD-SOI |

Depleção parcial da camada de silício. Aplicado em aplicações de alto desempenho e baixo consumo de energia (por exemplo, móveis, RF). |

3 SOI versus wafers de silício, quais são melhores?

A tecnologia Silicon-on-Insulator (SOI) e os tradicionais wafers de silício há muito tempo são fundamentais para moldar o cenário da fabricação de semicondutores, cada um com atributos estruturais e recursos de desempenho distintos. À medida que cresce a demanda por dispositivos eletrônicos mais eficientes, mais rápidos e menores, torna-se fundamental compreender as diferenças entre esses dois materiais fundamentais. Essa comparação busca destacar as nuances estruturais e os resultados de desempenho dos wafers de SOI e de silício.

3.1 Como as pastilhas de SOI e de silício diferem em sua estrutura

Pastilha de silício: Uma pastilha de silício convencional consiste em um único cristal de silício e em uma estrutura de silício monocristalino. Em um wafer de silício tradicional, a superfície do wafer é geralmente um único cristal de silício sem nenhuma camada isolante adicional. Os wafers de silício têm uma estrutura simples e são o substrato mais comum para dispositivos semicondutores.

SOI: na estrutura SOI, a superfície do wafer de silício é coberta por uma camada de material isolante (geralmente dióxido de silício). Essa camada de material isolante é normalmente usada para isolar a camada de silício do substrato de silício, reduzindo assim a interferência entre os dispositivos e melhorando o desempenho e a confiabilidade do dispositivo. Na parte superior da camada isolante, outra camada de silício é cultivada para formar uma estrutura de camada de silício - camada isolante - substrato de silício. A camada de silício é a camada ativa do transistor e geralmente tem as propriedades eletrônicas e o desempenho do dispositivo desejados. A espessura da camada isolante pode ser ajustada de acordo com os requisitos da aplicação para controlar as características e o desempenho do dispositivo.

Os SOIs têm uma camada isolante adicional em comparação com os wafers de silício convencionais. A presença dessa camada isolante melhora o desempenho e a confiabilidade do dispositivo, mas também aumenta a complexidade e o custo de fabricação.

3.2 Como as pastilhas de silício e SOI diferem em desempenho

- Supressão de diafonia: Cada transistor na estrutura SOI é isolado por uma camada isolante, reduzindo significativamente os efeitos de diafonia entre os dispositivos. Devido à presença da camada isolante, o efeito de acoplamento eletromagnético entre os transistores é reduzido, o que melhora o desempenho e a confiabilidade do dispositivo. A diafonia é geralmente um problema sério em circuitos integrados de alta densidade, e o uso de SOIs reduz efetivamente o efeito da diafonia no desempenho do dispositivo.

- Vantagens de velocidade e potência: Os dispositivos SOI normalmente têm maior velocidade e menor eficiência energética. Devido à resistência reduzida ao movimento de carga na estrutura SOI, os elétrons na camada de silício podem se mover mais rapidamente, resultando em velocidades de comutação mais altas e menor consumo de energia. Isso dá à SOI uma clara vantagem em aplicações de alto desempenho e baixo consumo de energia, como comunicações móveis e computação de alto desempenho.

- Maior resistência à radiação: A estrutura SOI melhora a resistência à radiação do dispositivo, tornando-o mais adequado para aplicações em ambientes de alta radiação. Devido à presença de uma camada isolante, os dispositivos SOI são menos sensíveis à radiação e, portanto, têm uma ampla gama de aplicações no espaço, em usinas nucleares e em outros dispositivos eletrônicos em ambientes de alta radiação. A resistência aprimorada à radiação é crucial para algumas aplicações específicas, como aeroespacial espacial e energia nuclear.

3.3 Como a SOI e os wafers de silício são usados

--Áreas de aplicação da SOI

Aplicações de alto desempenho: A SOI é frequentemente usada em aplicações que exigem alto desempenho, como chips de computador de alta velocidade e processadores gráficos. Suas características de baixa impedância de movimento de carga e supressão de diafonia o tornam ideal para obter alto desempenho.

Aplicações de baixo consumo de energia: Como os dispositivos SOI têm menor consumo de energia e velocidades de comutação mais altas, eles têm uma ampla gama de aplicações em áreas como dispositivos móveis e redes de sensores sem fio que exigem baixo consumo de energia. Por exemplo, os chips em dispositivos como smartphones e tablet PCs geralmente utilizam a tecnologia SOI.

Aplicações de radiofrequência (RF): As características de alta velocidade e baixa perda da SOI lhe conferem uma enorme vantagem em aplicações de radiofrequência (RF). Por exemplo, os dispositivos SOI podem ser usados para fabricar módulos front-end de RF de alto desempenho, interruptores de antena, amplificadores de potência e muito mais.

Aplicações em ambientes de alta radiação: A estrutura SOI melhora a resistência à radiação do dispositivo, o que a torna importante para aplicações no espaço, em usinas de energia nuclear e em outros ambientes de alta radiação. Por exemplo, sondas espaciais, sistemas de comunicação via satélite e outros dispositivos que precisam funcionar em um ambiente de alta radiação geralmente usam a tecnologia SOI.

--Aplicações tradicionais de wafer de silício

Os wafers de silício tradicionais são amplamente utilizados na fabricação de vários circuitos integrados, incluindo microprocessadores, memórias, sensores e assim por diante. Os wafers de silício são a base para a fabricação de circuitos integrados (CIs). Vários tipos de CIs, inclusive microprocessadores, memórias, circuitos analógicos, circuitos digitais etc., são fabricados por meio de camadas de diferentes materiais e circuitos em pastilhas de silício. Quase todos os dispositivos eletrônicos usarão chips tradicionais de fabricação de pastilhas de silício, como computadores pessoais, eletrodomésticos e sistemas eletrônicos automotivos. Ele também pode ser usado para fabricar uma variedade de dispositivos eletrônicos comumente usados em campos industriais, células solares e dispositivos biomédicos. Devido às excelentes propriedades semicondutoras, bem como aos processos de produção maduros e ao controle de qualidade estável, as pastilhas de silício são amplamente usadas em processos de produção e pesquisa, e o limite tecnológico também é menor em comparação com a SOI.

3.4 Como a SOI e os wafers de silício são produzidos

--Métodos de preparação de cristais de SOI

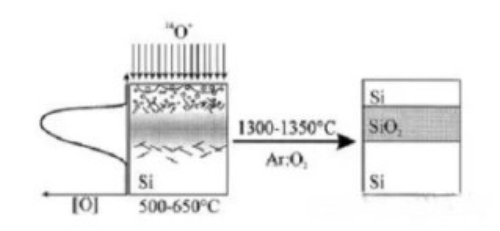

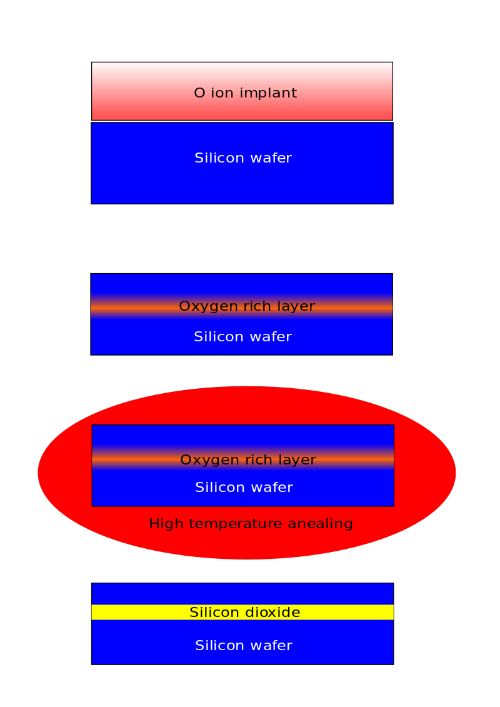

3.4.1 Tecnologia SIMOX

A tecnologia SIMOX, abreviação de Separation by IMplantation of OXygen (separação por implantação de oxigênio), é um dos métodos pioneiros de preparação de wafers SOI (Silicon-On-Insulator). Essa técnica utiliza a implantação de íons para introduzir íons de oxigênio no silício, formando uma camada de isolamento de óxido enterrada. Essa camada de óxido enterrado isola efetivamente o substrato da camada superior de filme fino de silício. O processo envolve a injeção de íons de oxigênio no wafer de silício abaixo da superfície, normalmente com um nível de energia de 200 keV e uma dose de 1,8 × 10^18 cm^-2. Em seguida, um processo de recozimento em alta temperatura, com duração de 3 a 6 horas a 1350°C, facilita as reações químicas entre os íons de oxigênio e os átomos de silício dentro do wafer, resultando na formação de uma camada isolante de dióxido de silício com espessura inferior a 240 nm abaixo da superfície. Acima dessa camada isolante, forma-se uma camada de silício cristalino, resultando na estrutura SOI composta por filme fino de silício - camada isolante de dióxido de silício - substrato de silício.

As vantagens da tecnologia SIMOX incluem a formação de uma camada de óxido enterrado (BOX) relativamente uniforme. A espessura da camada de silício sobre a BOX pode ser controlada com precisão por meio do gerenciamento da energia de injeção. Além disso, a interface entre a BOX e a camada superior de silício permanece notavelmente plana.

No entanto, a tecnologia SIMOX tem suas limitações. A faixa para ajuste da espessura da BOX e da camada superior de silício é relativamente limitada. Normalmente, a espessura da CAIXA não excede 240 nm, pois camadas excessivamente finas podem levar à ruptura entre a camada superior e o substrato, acompanhada pelo aumento da capacitância parasita. Da mesma forma, a espessura do filme de silício superior geralmente é limitada a 300 nm, o que exige um dispendioso crescimento de silício epitaxial e o subsequente tratamento de achatamento por polimento químico-mecânico (CMP). Além disso, o SIMOX pode induzir danos ao filme de superfície, e a qualidade do cristal do filme de silício superior pode não corresponder à do silício de cristal único em massa. Além disso, a qualidade do cristal do SiO2 enterrado é inferior à obtida por meio da oxidação térmica. A implementação do SIMOX exige equipamentos especializados de implantação de íons, como máquinas caras de injeção de oxigênio de grande fluxo de feixe, além de processos prolongados de recozimento em alta temperatura, o que contribui para aumentar os custos de produção.

3.4.2 Tecnologia BESOI

A tecnologia BESOI (Bond and Etch Back Silicon-On-Insulator) consiste em unir dois wafers, criando uma camada de dióxido de silício como camada de óxido enterrada entre eles. Posteriormente, a tecnologia de back-engraving é empregada para ajustar com precisão a espessura de um wafer para formar a espessura desejada para os wafers SOI.

O processo BESOI começa com o tratamento de um wafer (wafer A) com oxidação térmica, criando uma camada de óxido, enquanto o outro wafer (wafer B) é submetido a uma ligação de baixa temperatura com a superfície oxidada do wafer A. Esse processo de ligação, conhecido como Silicon Fusion Bonding (SFB), envolve várias etapas:

Tratamento hidrofílico: Os dois wafers são submetidos a um tratamento hidrofílico de baixa temperatura (400°C) para induzir a formação de ligações de hidroxila (OH) em suas superfícies.

Ligação por meio da força de Van der Waals: As duas pastilhas são então colocadas em contato, e as ligações OH facilitam sua ligação por meio da força de Van der Waals.

Recozimento térmico: O recozimento térmico de alta temperatura (1100°C) é realizado para afastar os íons de hidrogênio, promovendo a formação de ligações Si-O-Si na interface ligada, reforçando assim a ligação.

Back-etching: o excesso de silício de um wafer é removido usando a tecnologia de back-engraving, deixando para trás a espessura desejada para o filme fino de silício superior. O recozimento e o polimento químico-mecânico (CMP) subsequentes garantem a formação de uma superfície lisa e limpa para os wafers SOI.

A tecnologia BESOI oferece várias vantagens em relação à tecnologia SIMOX. Por exemplo, ela evita problemas relacionados a danos por injeção e garante a formação de uma camada de óxido enterrada termicamente oxidada com menor densidade de defeitos e densidade de pinhole. Além disso, o filme de silício superior produzido por meio da BESOI consiste em silício monocristalino de alta qualidade, o que melhora o desempenho geral do dispositivo.

Entretanto, a tecnologia BESOI também apresenta desafios. É difícil obter filmes de silício muito finos, e o controle dos defeitos da interface e da homogeneidade do filme de silício superior continua sendo um desafio. Além disso, o processo envolve etapas de back-engraving e CMP de alto custo, o que leva a um desperdício significativo de material de wafer, que não pode ser reciclado e contribui para aumentar os custos de produção.

3.4.3 Tecnologia Smart-Cut

A tecnologia Smart-Cut é derivada da BESOI: Primeiro, duas pastilhas de silício são preparadas; uma das pastilhas é oxidada termicamente para formar uma camada de SiO2 e, em seguida, íons de hidrogênio são injetados no substrato da pastilha; a outra pastilha não precisa ser processada; semelhante à BESOI, as duas pastilhas são unidas; após a ligação, os wafers injetados com íons de hidrogênio se quebram na interface enriquecida com íons de hidrogênio por meio de uma reação térmica a 400-600 °C; por fim, a interface entre a superfície quebrada e a camada de óxido forma uma camada de filme de silício após o tratamento de alta temperatura (1100 °C) para afastar os íons de hidrogênio. Após a ligação, os wafers injetados com íons de hidrogênio fraturarão no ponto de enriquecimento de íons de hidrogênio, e uma camada de película fina de silício será formada entre a superfície da fratura e a camada de óxido; finalmente, após o tratamento de alta temperatura (1100 °C), os íons de hidrogênio são expulsos, de modo que a interface ligada formará uma ligação Si-O-Si, que fortalecerá a ligação química e melhorará a qualidade da camada de película fina de silício, e então a superfície será aplainada pelo tratamento CMP.

O Smart-Cut é semelhante ao BESOI, pois o filme de silício superior é silício em massa e a BOX é um filme oxidado termicamente. A espessura da camada da CAIXA e do filme de silício superior pode ser ajustada em uma ampla faixa, e a espessura do filme de silício superior é controlada pela utilização da energia da implantação de íons, de modo que o filme de silício superior com espessura muito fina e boa uniformidade pode ser obtido. Além disso, o material do wafer decapado pode ser reutilizado, o que permite a redução de custos.

--Método de preparação de cristais de wafer de silício

O método Czochralski é amplamente empregado para o crescimento de cristais de silício, aproveitando um cadinho cheio de silício aquecido para manter uma temperatura de 1685°C. Essa temperatura excede o ponto de fusão do silício. Essa temperatura excede o ponto de fusão do silício em cerca de 100°C, tornando o silício no cadinho fundido. Na parte superior do cadinho, há uma haste de elevação, com um dispositivo mecânico que permite que ela se eleve e gire livremente. Um pequeno pedaço de silício monocristalino, que funciona como uma "semente", é afixado no topo da alavanca. Esse cristal semente inicia a atração dos átomos de silício ao redor, organizando-os em uma estrutura de cristal. À medida que o cristal sobe e gira gradualmente, as seções extraídas permanecem parte do mesmo cristal único. O grande cristal único resultante mede até 200 milímetros de diâmetro, mais espesso do que um braço médio. Esse cristal não apresenta interfaces ou defeitos, resumindo a perfeição máxima que pode ser alcançada em cristais únicos produzidos pelo homem.

Para garantir a pureza do material e evitar a nucleação não uniforme, todas as operações devem ocorrer sob vácuo ou proteção de gás inerte. As técnicas tradicionais de elevação de silício monocristalino envolvem a iniciação de um pescoço fino no início do crescimento do cristal, denominado "método de necking", para evitar deslocamentos do cristal. No entanto, os avanços na tecnologia de semeadura, especialmente a infusão de uma quantidade significativa de boro no cristal de semente, aumentaram consideravelmente sua resistência, evitando a necessidade de um pescoço de 3 mm de diâmetro. Essa abordagem inovadora substitui o método de pescoço de três décadas atrás, não apenas facilitando a produção de silício de cristal único grande, mas também reduzindo os tempos de crescimento do cristal e aumentando os rendimentos, abrindo assim possibilidades para a produção econômica de circuitos integrados de escala ultragrande.

No crescimento de wafer, o polissilício é introduzido em um cadinho de quartzo dentro de um forno, seguido de vácuo ou purga de gás inerte para criar um estado fundido. Depois que o silício derretido se estabiliza, os cristais únicos podem ser puxados usando a direção interna do cristal de uma semente predeterminada como guia na superfície do líquido. Por meio do controle preciso da altura da superfície líquida do cadinho, da temperatura da interface sólido-líquido e da velocidade de rotação do cristal de semente, o silício é transformado de líquido em sólido, garantindo uma direção cristalina interna uniforme para o crescimento de cristais únicos de grande diâmetro. Os processos de ajuste automático controlados por computador e as velocidades de elevação garantem o crescimento isotrópico do silício monocristalino.

Tabela 2 Wafers SOI versus Wafers de silício

|

Pastilha de silício |

Pastilha de SOI |

||

|

Estrutura |

Sem camada isolante |

Camada isolante |

|

|

Desempenho |

Supressão de diafonia |

Não |

Sim |

|

Velocidade e potência |

Menor e maior |

Maior e menor |

|

|

Resistência à radiação |

Inferior |

Maior |

|

|

Aplicações |

Circuitos integrados |

Aplicações de alto desempenho |

|

|

Células solares |

Aplicações de baixo consumo de energia |

||

|

Dispositivos biomédicos |

Ambientes de alta radiação |

||

|

Preparação e custo |

Método Czochralski |

SIMOX/BESOI/Smart-cut |

|

|

Conveniente |

Intrincado |

||

|

Baixo custo |

Alto custo |

||

4 Conclusão

Existem diferenças significativas entre os wafers de SOI e de silício em termos de estrutura do material, características de desempenho, áreas de aplicação etc. A estrutura SOI melhora o desempenho e a confiabilidade do dispositivo por meio de uma estrutura de substrato de silício com camada isolante e camada de silício em camadas, mas a um custo de fabricação mais alto. Em contrapartida, a fabricação tradicional de pastilhas de silício é mais barata e adequada para uma ampla gama de fabricação de circuitos integrados. Portanto, ao selecionar uma estrutura de material, as vantagens e desvantagens da SOI e dos wafers de silício devem ser avaliadas de forma abrangente com base em requisitos de aplicações específicas e considerações de custo para obter o melhor desempenho e benefícios econômicos.

Leitura relacionada:

O impacto da qualidade do wafer de silício no desempenho e na confiabilidade dos semicondutores

Referências:

[1]Jin W ,Wei C ,Wanghua Z , et al. Otimização e comparação abrangente do deslocador de fase termo-óptico com guia de onda dobrado nas plataformas SiN e SOI[J]. Optics Communications,2024,555.

[Xin F, Jiaqi N, Shanglin Y, et al. Filtros ópticos de entalhe com comprimento de onda central ajustável e faixa espectral livre reconfigurável na plataforma SOI. Optics Communications,2024,554.

[3]N. V ,A. M ,I. K , et al. Novel crossbar array of silicon nitride resistive memories on SOI enables memristor rationed logic[J]. Solid State Electronics,2024,211.

Barras

Barras

Miçangas e esferas

Miçangas e esferas

Parafusos e porcas

Parafusos e porcas

Cadinhos

Cadinhos

Discos

Discos

Fibras e tecidos

Fibras e tecidos

Filmes

Filmes

Flocos

Flocos

Espumas

Espumas

Folha de alumínio

Folha de alumínio

Grânulos

Grânulos

Favos de mel

Favos de mel

Tinta

Tinta

Laminado

Laminado

Nódulos

Nódulos

Malhas

Malhas

Filme metalizado

Filme metalizado

Placa

Placa

Pós

Pós

Vara

Vara

Folhas

Folhas

Cristais individuais

Cristais individuais

Alvo de pulverização

Alvo de pulverização

Tubos

Tubos

Lavadora

Lavadora

Fios

Fios

Conversores e calculadoras

Conversores e calculadoras

Chin Trento

Chin Trento